Product Summary

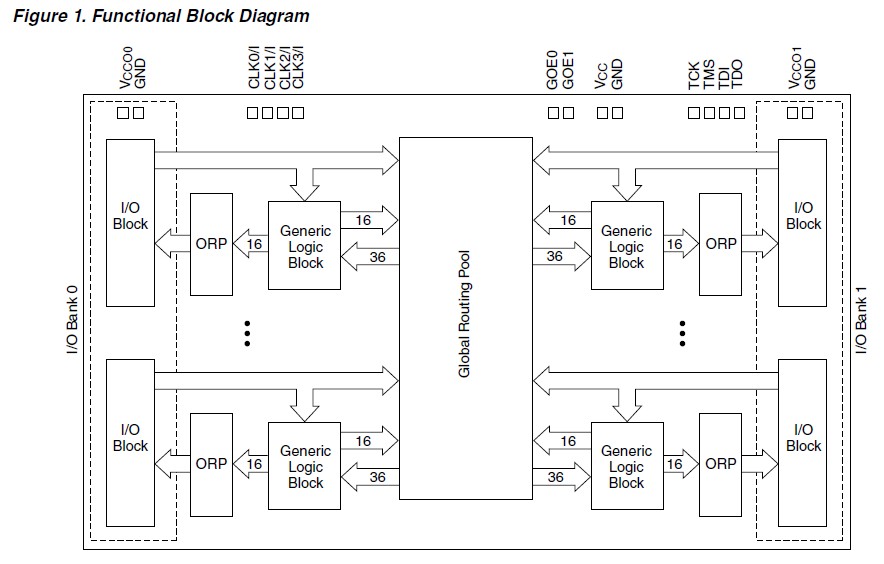

The LC4128V75T100-10I is an in-system programmable superFAST with high density PLD. The high performance LC4128V75T128-10I from Lattice offers a SuperFAST CPLD solution. Retaining the best of both families, the LC4128V75T128-10I architecture focuses on significant innovations to combine the highest performance with low power in a flexible CPLD family. The LC4128V75T128-10I combines high speed and low power with the flexibility needed for ease of design. With its robust Global Routing Pool and Output Routing Pool, this family delivers excellent First-Time-Fit, timing predictability, routing, pin-out retention and density migration.

Parametrics

LC4128V75T128-10I absolute maximum ratings: (1)Supply Voltage (VCC): -0.5 to 2.5V; (2)Output Supply Voltage (VCCO): -0.5 to 4.5V; (3)Input or I/O Tristate Voltage Applied4, 5: -0.5 to 5.5V; (4)Storage Temperature: -65 to 150℃; (5)Junction Temperature (Tj) with Power Applied: -55 to 150℃.

Features

LC4128V75T128-10I features: (1)High Performance; (2)Enhanced macrocells with individual clock, reset, preset and clock enable controls; (3)Up to four global OE controls; (4)Individual local OE control per I/O pin; (5)Excellent First-Time-Fit TM and refit; (6)Fast path, SpeedLocking TM Path, and wide-P path; (7)Wide input gating (36 input logic blocks) for fast counters, state machines and address decoders.

Diagrams

|

LC4100C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LC4101C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LC4102C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LC4104C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LC4105V |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LC4115 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)